| UNIVERSITY OF VAASA                                                                 |                |  |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------|--|--|--|--|--|

| FACULTY OF TECHNOLOGY                                                               | •              |  |  |  |  |  |

| AUTOMATION TECHNOLOG                                                                | Y              |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

| Kim Berg                                                                            |                |  |  |  |  |  |

| EVALUATION OF SYSTEMVERILOG AND CONSTRAINED RANDOM VERIFICATION FOR DIGITAL DESIGNS |                |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

|                                                                                     |                |  |  |  |  |  |

| V. 2010                                                                             |                |  |  |  |  |  |

| Vaasa 2018                                                                          |                |  |  |  |  |  |

| Supervisor                                                                          | Jarmo Alander  |  |  |  |  |  |

| Instructor                                                                          | Petri Ylirinne |  |  |  |  |  |

### **FOREWORD**

The purpose of this thesis was to evaluate verification methods for Field Programmable Gate Arrays with an aim to improve the testing of digital designs at Danfoss Drives. I want to thank the supervisor of this thesis, professor Jarmo Alander, and the instructor, MSc Petri Ylirinne, for providing valuable guidance and support throughout the process of writing this study.

# TABLE OF CONTENTS

| FO | REW | ORD                           |                                                              | 2  |

|----|-----|-------------------------------|--------------------------------------------------------------|----|

| TA | BLE | OF CO                         | NTENTS                                                       | 3  |

| 1  | INT | RODU                          | ICTION                                                       | 9  |

| 2  | TH  | EORY A                        | AND BACKGROUND                                               | 12 |

| 3  | VE  | RIFICA                        | ATION CONCEPTS OF THIS STUDY                                 | 17 |

|    | 3.1 | Const                         | rained Random Verification and Coverage Driven Verification  | 17 |

|    |     | 3.1.1                         | The Hardwave Verification Language features of SystemVerilog | 18 |

|    |     | 3.1.2                         | Transaction Level Modeling                                   | 19 |

|    |     | 3.1.3                         | The Universal Verification Methodology                       | 20 |

|    |     | 3.1.4                         | Self-checking test benches                                   | 24 |

|    | 3.2 | Temporal Logic verification   |                                                              |    |

|    |     | 3.2.1                         | SystemVerilog Assertions                                     | 29 |

|    |     | 3.2.2                         | Assertions used as protocol checkers                         | 32 |

|    |     | 3.2.3                         | Using assertions to complement test benches                  | 32 |

| 4  | PRI | ESENT                         | TESTING METHODS OF THE COMPANY                               | 34 |

|    | 4.1 | Simul                         | ation-based test types in use                                | 34 |

|    | 4.2 | 2 Verification methods in use |                                                              |    |

|    | 4.3 | Test re                       | eporting with code coverage                                  | 36 |

| 5  | VE  | RIFICA                        | ATION STRATEGY                                               | 39 |

|    | 5.1 | Verifi                        | cation strategies for the IP-block test                      | 39 |

|    |     | 5.1.1                         | Full IP test bench                                           | 40 |

|     |           | 5.1.2                                                         | Divide and conquer test bench                                   | 43   |

|-----|-----------|---------------------------------------------------------------|-----------------------------------------------------------------|------|

|     | 5.2       | Verification strategy for the integration test                |                                                                 |      |

|     | 5.3       | Functi                                                        | onal coverage                                                   | 47   |

| 6   | CAS       | SE STU                                                        | UDIES                                                           | 48   |

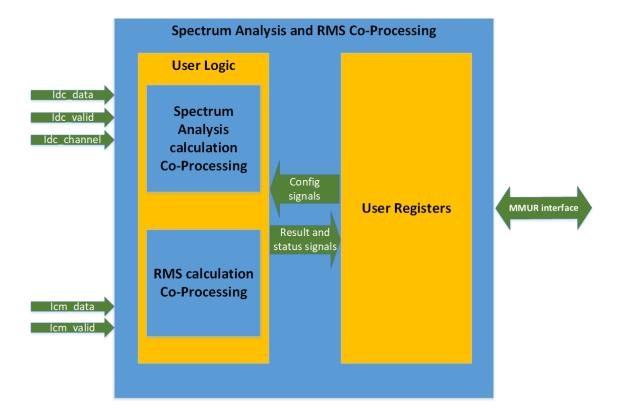

|     | 6.1<br>IP | Testin<br>48                                                  | g the Discrete Root Mean Square and Spectrum Analyser co-proces | sing |

|     |           | 6.1.1                                                         | Functional description of the IP                                | 48   |

|     |           | 6.1.2                                                         | The verification plan                                           | 50   |

|     |           | 6.1.3                                                         | The full IP test bench                                          | 53   |

|     |           | 6.1.4                                                         | Test cases of the full IP test bench                            | 53   |

|     |           | 6.1.5                                                         | Building the full IP test bench                                 | 55   |

|     |           | 6.1.6                                                         | Building the divide and conquer test benches                    | 66   |

|     | 6.2       | Testing the priority arbitrated full-duplex communication SUT |                                                                 | 71   |

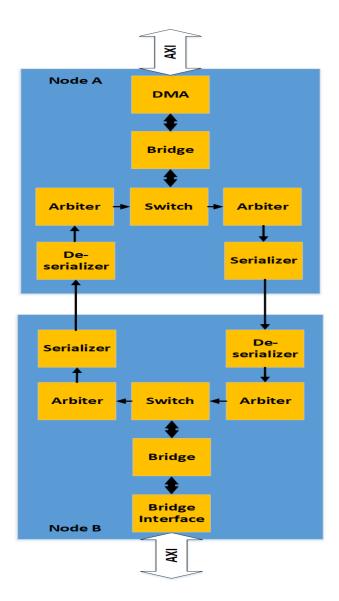

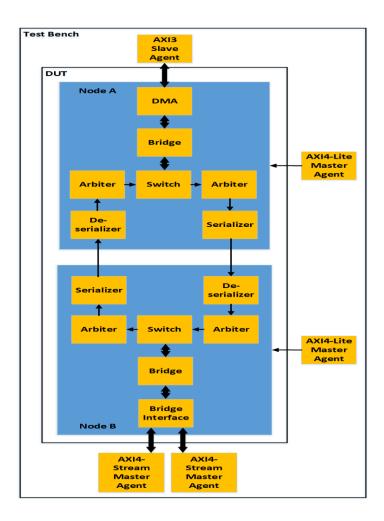

|     |           | 6.2.1                                                         | Functional description of the SUT                               | 72   |

|     |           | 6.2.2                                                         | The verification plan                                           | 74   |

|     |           | 6.2.3                                                         | Building the NBNA-test                                          | 76   |

| 7   | RES       | SULTS                                                         |                                                                 | 84   |

|     | 7.1       | Results of the full IP test bench case study                  |                                                                 | 84   |

|     | 7.2       | Results of the divide and conquer method                      |                                                                 | 87   |

|     | 7.3       | Result                                                        | s of the system level test case study                           | 91   |

| 8   | CO        | NCLUS                                                         | SIONS                                                           | 93   |

| LIS | T OF      | REFE                                                          | RENCES                                                          | 98   |

### SYMBOLS AND ABBREVIATIONS

MHz Megahertz

ms Millisecond

ABV Assertion Based Verification

AC Alternating Current

AD Analog to Digital

ADC Analog to Digital Converter

ALU Arithmetic Logic Unit

ASIC Application Specific Integrated Circuit

AXI Advanced Extensible Interface

BFM Bus Functional Model

CDV Coverage Driven Verification

CRV Constrained Random Verification

DC Direct Current

DMA Direct Memory Access

DRMS Discrete Root Mean Square

DUT Design Under Test

FEC Focused Expession Coverage

FIFO First In First Out

FPGA Field Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

HVL Hardware Verification Language

IP Intellectual Property

MMUR Memory Mapped User Register

OOP Object-Oriented Programming

PSL Property Specification Language

PWM Pulse Width Modulation

RTL Register Transfer Level

SA Spectrum Analyser

SoC System on a Chip

SUT System Under Test

SVA SystemVerilog Assertions

TDD Test Driven Development

TLM Transaction Level Modeling

UVM Universal Verification Methodology

VFD Variable Frequency Drive

VIF Virtual Interface

VIP Verification Intellectual Property

VHDL Very High Speed Integrated Circuit Hardware Description

Language

UNIVERSITY OF VAASA

Faculty of technology

**Author:** Kim Berg

**Topic of the Thesis:** Evaluation of SystemVerilog and Constrained Ran-

dom Verification for Digital Designs

**Pages: 100**

**Supervisor:** Professor Jarmo Alander **Instructor:** MSc Petri Ylirinne

**Degree:** Master of Science in Technology

**Major of Subject:** Automation Technology

Year of Entering the University: 2012 Year of Completing the Thesis: 2018

The Field Programmable Gate Array is a device that consists of configurable logic, on chip-memory and often functionality that is fixed into silicon, such as hardware multipliers or transceivers for peripheral communication. The Field Programmable Gate Array is a configurable and reprogrammable digital circuit that can be designed to implement functionality that is deterministic and parallel. Due to these qualities the Field Programmable Gate Array is also an energy efficient choice of hardware for many digital designs.

Technological advancements in the semiconductor industry have resulted in a continuous decrease in transistor sizes, which in turn has allowed for an increased transistor density in semiconductor devices. For Field Programmable Gate Arrays the development has led to increasingly complex designs, as an increased amount of programmable resources are available. Consequently, the time and effort spent in verification of the digital designs has increased. Discovering design flaws before end products are released is not only economically crucial, but a failure to do so might damage the reputation of a company. In this thesis current verification trends are evaluated in three case studies made for Danfoss Drives. The objective of the thesis is to determine whether the quality of testing of Field Programmable Gate Array designs at the company can be improved by using Constrained Random Verification and the SystemVerilog language. Test benches for behavioral simulations are built using SystemVerilog in conjunction with the Universal Verification Methodology.

Constrained Random Verification based on the SystemVerilog language and the Universal Verification Methodology was evaluated for unit level testing in two case studies for one Intellectual Property core. A third case study was made for a system level design of multiple Intellectual Property cores as a SystemVerilog test bench utilizing neither constrained randomization nor the Universal Verification Methodology. Improved test coverage and an increased degree of automatization was achieved for the unit level testing, although at the cost of an increased verification effort. In the system level testing the capabilities of the SystemVerilog language proved beneficial, especially for creating transaction level stimulus, writing self-checking mechanisms for the test bench and modularizing its structure.

**KEYWORDS:** Field Programmable Gate Array, Verification, Constrained Random Verification, SystemVerilog, The Universal Verification Methodology

## VAASAN YLIOPISTO

Teknologian ja innovaatiojohtamisen yksikkö Tekijä: Kim Berg

**Diplomityön nimi:** SystemVerilogin ja Painotetun

Satunnaistamistestauksen Arviointi Digitaalipiireille

Valvoja: Professori Jarmo Alander

Ohjaaja:DI Petri YlirinneTutkinto:Diplomi-insinööriPääaineAutomation Technology

Opintojen aloitusvuosi: 2012

Diplomityön valmistumisvuosi: 2018 Sivumäärä: 100

Field Programmable Gate Array on laite joka koostuu ohjelmoitavasta logiikasta, sisäisestä muistista ja usein myös toiminnallisuudesta joka on kiinteästi sidottu laitteistoon, kuten kertolaskupiirit tai lähetin-vastaanotimmet ulkoista viestintää varten. Field Programmable Gate Array on konfiguroitava ja uudelleenohjelmoitava digitaalinen piiri joka voidaan suunnitella toteuttamaan toiminnallisuutta joka on determinististä ja rinnakkaista. Näistä ominaisuuksista johtuen, Field Programmable Gate Array on myös energiatehokas laitteistovalinta monen digitaalipiirin mallinnukseen.

Tekninen kehitys puolijohdeteollisuudessa on johtanut jatkuvaan transistorikokojen pienenemiseen, mikä puolestaan on sallinut suuremman transistoritiheyden puolijohdelaitteissa. Piireille mahtuvien resurssien kasvaessa myös Field Programmable Gate Array laitteiden mallit ovat monimutkaistuneet. Tästä johtuen, suunniteltujen digitaalipiirien verifiointiin kuluva aika ja vaiva on kasvanut. Suunnitteluvirheiden löytäminen tuotteesta ennen sen julkistamista ei ole valmistajalle ainoastaan taloudellisesti tärkeää, vaan saattaa epäonnistuessaan myös olla haitaksi valmistajan maineelle. Tässä tutkimuksessa ajankohtaisia verifiointitrendejä on arvioitu kolmessa Danfoss Drivesille toteutetussa tapaustutkimuksessa. Tutkimuksen tavoitteena on arvioida Painotetun Satunnaistamistestauksen ja SystemVerilog-kielen hyödyn Danfoss Drivesille toteutettujen Field Programmable Gate Array mallien verifioinnissa. Käyttäytmissimulointeja varten mallinnetut testipenkit toteutetaan SystemVerilog-kielellä käyttäen metodologiana Universal Verification Methodologya.

SystemVerilogiin ja Universal Verification Methodologyyn pohjautuvaa Painotettua Satunnaistamistestausta on arvioitu yksikkötestaukselle kahdessa tapaustutkimuksessa yhdelle Intellectual Property lohkolle. Kolmas tapaustutkimus on toteutettu järjestelmätason testaukselle useamman Intellectual Property lohkon järjestelmälle ilman painotettua satunnaistamista tai Universal Verification Methodologya. Yksikkötason testauksessa testikattavuuksia onnistuttiin kohottamaan Verifiointiin panostettu aika kuitenkin kasvoi. testiautomaation aste kasvoi. testauksessa SystemVerilogin kieliominaisuudet hyödylliseksi, etenkin transaktiotason testisyötteen kirjoittamisessa, automaattisessa vasteentarkistuksessa ja testipenkin modulaarisen rakenteen mallintamisessa.

KEYWORDS: Field Programmable Gate Array, Verifiointi, Painotettu Satunnaistamistestaus, SystemVerilog, The Universal Verification Methodology

### 1 INTRODUCTION

The Field Programmable Gate Array, or FPGA, is a digital circuit that contains configurable logic blocks, on-chip memory and often functionality that is fixed into silicon, such as hardware multipliers or transceivers for peripheral communication. The configurable logic of the FPGA can be designed to implement functionality that is deterministic and parallel. As a result of this parallelism, FPGAs can achieve high throughput for data handling in tasks such as digital signal processing. An essential feature of the FPGA is that it is not only configurable, but also reconfigurable. Compared to conventional integrated circuit architectures, such as the Application Specific Integrated Circuit (ASIC), the FPGA offers a solution that is cheaper and faster to design (Maxfield 2004: xiii-xiv). On the other hand, the unit cost of an FPGA chip is generally higher than for a non-reconfigurable integrated circuit. FPGA designs are modelled using Hardware Description Languages (HDL), such as Verilog or the Very High Speed Integrated Circuit Hardware Description Language (VHDL). These languages have features to model concurrent behavior, which is most often synchronized by a clock. A processor, in contrast, is inherently sequential and performs tasks over multiple clock cycles. Although the processor generally achieves higher clock speeds than an FPGA, it usually underperforms in comparison with the FPGA when throughput, parallelism and energy efficiency is concerned.

A drawback of programmable logic is the effort that goes into modeling a functional design. Reduced transistor sizes have resulted in increased resource availability in FPGA chips, which in turn has allowed for a greater amount of design units and signals to be fit into a system-wide design. Consecutively, the complexity of the digital designs has increased. This trend has also affected the verification process. Verification, by definition, is the process of validating that a product or system meets the requirements and specifications that have been set for it. Verification is therefore an important part of quality control, and if done poorly, might be economically damaging for a company. For digital designs finding design flaws as early as possible is vital. In the development process a bug that goes unnoticed during unit tests is likely to be much harder to find once the tests move to the system level. In the worst case the bug is not found until the

product has been released onto the market, in which case the reputation of the company is in high risk to suffer. For safety critical designs there is an additional concern as there might even be life-threatening consequences of poorly performed verification.

The verification of FPGA designs can be performed as either testing with the real hardware, with the design running on the target device, or as a simulation that is performed in a simulator tool. The former has the benefit of being able to validate that the actual design works as intended. However, what hardware testing lacks is the visibility into the design. When a bug is discovered and the debugging work is started, the effectiveness of the process will be limited by the amount of signals that can be made visible through the external pins of the target device or by the amount of signals supported by an internal logic analyzer. Simulations, on the other hand, are generally capable of accessing all signals of the design, whether they are peripheral signals or internal to the design. Another benefit of simulation-based testing is the increased ability to model stimulus that extensively covers the functionality of the Design Under Test (DUT). For a simulation a test bench is made that resembles its counterpart in hardware testing – it creates stimulus to the DUT while also monitoring the response from it. The test bench of the simulation is, however, written as code and is not dependent on hardware. The challenge of simulation-based testing is, naturally, to create a test bench of good quality. A test bench can be considered of good quality if it stimulates the design with realistic stimulus, creates stimulus that extensively covers the functionality of the design and reliably reports the results of the response generated by the DUT.

The objective of this thesis is to evaluate the use of Constrained Random Verification (CRV) and the SystemVerilog language for simulation-based verification of FPGA designs. The methodology of choice for the CRV evaluation is the Universal Verification Methodology (UVM), which has become increasingly common for verification of ASIC and FPGA designs. Verification strategies will be made for the proposed verification methodologies, after which case studies will be performed for unit and system level testing. The goal of these strategies is to improve the quality of testing by suggesting methods that will raise test coverages while automating the test process. In order to establish a theoretical framework for this thesis, previously written papers related to eval-

uation of CRV methods are used for reference. Guidelines for writing the test benches of the case studies in this thesis have mainly been acquired from the *UVM cookbook* by Mentor Graphics (2012) and *SystemVerilog for Verification* by Chris Spear and Greg Tumbush (2012). The expectations for this thesis have been established by reviewing three theses that were all studies of CRV evaluation done with SystemVerilog. In all of these theses CRV testing was evaluated, either for a company or as a university study. The findings of these studies will be discussed in Chapter 2, where further information of the verification concepts of this study are presented. Finally, the feasibility of the verification strategies, the SystemVerilog language and CRV testing will be discussed. The results of the verification case studies will also be assessed.

### 2 THEORY AND BACKGROUND

A study of functional verification trends for ASIC and FPGA designs was conducted in 2016 by the Wilson Research Group. The findings of this study suggest that verification amounts to an increased percentage of the total time spent on both ASIC and FPGA designs (Mentor Graphics 2016). According to the study, in 2016 the amount of time spent on verification was 48% of the total amount of time spent on system implementation. Results from earlier years of the same study state that in 2014 the percentage of time spent on verification was 46% of the total time, and further back in 2012 it was 43%. Not surprisingly, this trend has also led to an increased number of verification engineers that are by average involved in FPGA projects. The average number of engineers per FPGA project was 6.6 in 2012, while in 2016 it had risen to 7.9. In 2012 only 2.6 out of the total 6.6 engineers were verification engineers. In 2016 the figure was 3.6 verification engineers versus 4.3 design engineers. However, although there is an increased effort into verification, bugs are still common. The study reveals that for safety critical FPGA designs, which can be assumed to undergo extensive verification, bugs escape into production in 75% of all cases. Another interesting finding by the study is that in 2016, 59% of all FPGA projects included one or more embedded processors.

The functional verification study also details trends related to the languages used for functional verification, the testing methodologies and the use of assertions. According to the study, as of 2016 SystemVerilog was the most preferred verification language. Among the methodologies, UVM, which defines a test bench architecture, as well as a set of classes and functions for it, has become the most popular verification methodology. In 2016, almost 50% of the companies participating in the study claimed to have used UVM in their test benches, and the projection for 2017 was that the percentage would rise over the 50% mark. Perhaps as a result of the increasing amount of companies that are implementing CRV methodologies such as UVM, the usage of code coverage and functional coverage, both of which will be discussed during this thesis, have also increased. Property checking assertions have also become increasingly common in verification. In 2016 the companies participating in the study claimed to have used assertions for over 45% of the FPGA designs they were verifying. In 2012 assertions were

used for only about 35% of the FPGA designs. The study suggests that the favored assertion language for FPGA designs is the SystemVerilog Assertions (SVA) subset of SystemVerilog.

Table 1. A summary over some of the FPGA-related findings presented in the 2016 Wilson Research Group study of functional verification trends. The asterisk sign denotes values that are approximations of chart table representations used in the study (Mentor Graphics 2016).

|                                                                                               | 2016 | 2014 | 2012 |

|-----------------------------------------------------------------------------------------------|------|------|------|

| Percentage of the total FPGA system implementation time that is spent on verification         | 48%  | 46%  | 43%  |

| Average number of engineers involved in an FPGA project                                       | 7.9  | 7.8  | 6.6  |

| Average number of verification engineers involved in an FPGA project                          | 3.6  | 3.5  | 2.6  |

| Percentage of FPGA design projects for which SystemVerilog is used in verification            | 47%* | 38%* | 31%* |

| Percentage of FPGA design projects for which UVM is used in verification                      | 47%* | 41%* | 32%* |

| Percentage of FPGA design projects for which code coverage is used as a coverage metric       | 64%* | 57%* | 52%* |

| Percentage of FPGA design projects for which functional coverage is used as a coverage metric | 56%* | 54%* | 42%* |

| Percentage of companies that have used assertions for FPGA verification                       | 46%* | 43%* | 35%* |

The functional verification topics covered by this thesis relate to FPGA designs in frequency converters manufactured by Danfoss Drives. The frequency converter is a device that converts an Alternating Current (AC) of one frequency to another. A common application target for frequency converters is between a power grid and an AC motor. In this setting the frequency converter is often called an AC drive or a Variable Frequency Drive (VFD), and it is used to adjust the speed of the motor by alternating its input frequency. There are several potential benefits of having optimal speed control for an AC motor, such as matching the power and torque requirements of a system or reducing mechanical stress on the machines in it. Another benefit of the AC drive is the energy saving potential it offers. According to Danfoss about 25% of all AC motors today are equipped with AC drives. Furthermore, the company estimates that for 40-50% of the

motors not yet equipped with drives there would be a potential for energy savings if AC drives were installed (Danfoss Drives 2016). The basic operation principle of an AC drive is to rectify an AC, store it as Direct Current (DC) to a capacitor and then invert it back to AC with a desired frequency. One of the main tasks of the FPGA in frequency converters is to generate the Pulse Width Modulation (PWM) signal that is used to invert DC to AC. As the FPGA is a deterministic and parallel device it is suitable for this task. FPGAs are also used for other time-critical tasks of the drives, such as low latency communication between various nodes of the device. Valid behavior of the FPGA designs is therefore crucial for the overall performance of the AC drive. Faulty PWM generation could cause motor failure in AC motors connected to the drive, while logical bugs in communication logic could lead to distorted data or data being lost.

At this stage of the study, some assumptions of the coming work are made. These assumptions are based on observations that are made in three studies that were chosen as a reference for the evaluation done in this paper. According to one of the papers, constrained randomized tests were able to discover obscure bugs that would have been hard to find with conventional directed tests. In this study from 2008 a verification team at the company in question was evaluating the use of SystemVerilog with a CRV methodology that can be considered a predecessor to UVM. The verification team was able to achieve greater automatization of testing and was eventually finding bugs that would have been challenging to find with their pre-existing test methodology, which was based on self-checking directed tests. According to the study there were no time penalties during the introduction of these new methods, however, it must be stated that the company, Rockwell Collins, already had a verification team that was doing testing for safety critical designs. It can therefore be assumed that the verification was already at a reasonably high level (Keithan, Landoll, Logan & Marriott 2008).

In the second paper, which was written as a company evaluation case study for Nokia Networks, an introduction of CRV with UVM is presented. In this paper the writer describes the verification process for a co-processor designed by the company. Although the verification effort is not described in great detail, the impression is that for a designer with no previous knowledge of CRV and UVM there will be a learning process that

is time consuming. In the study a team of two engineers were verifying the co-processor for a time well over one year and the testing was still not complete. However, the DUT of the study is a system-wide design that can be considered complex. The writer's estimation is that at the time of writing the study, the time spent in verification is already greater than 50% of the total time spent on the system implementation (Ihanajärvi 2016).

The third paper referenced for this thesis describes an introduction to UVM for unit testing. The study provides valuable insight into what challenges may be faced by a designer that is new to UVM. According to the paper the biggest challenge was the implementation of verification components that require synchronization between the class-based test bench and the DUT. Nonetheless, the raised level of abstraction that comes with UVM was regarded as an advantage, especially for speeding up the creation of test sequences by hiding away low-level signal specific details of the test bench. In addition, it is concluded that after the initial challenges faced in the implementation of the first test bench, the following test bench implementations are significantly easier and benefit from the reusability provided by UVM (Francesconi, Rodriguez & Julian 2014).

One of the theorized challenges of creating CRV test benches is the DUT predictor model implementation. The predictor model, which is the self-checking mechanism of the CRV test bench, will be discussed further in Chapter 3.1.4. Nevertheless, it is essentially the component of the test bench that automates the checking of response against the predicted response. Based on the experiences of Francesconi et. al., the theory is that the creation of a predictor model that is completely synchronized with the DUT and faultless could for some designs be a challenging task that requires plenty of design effort. The challenge is not only limited to functional verification of digital designs, as in fact the *digital twin*, a digital model of a physical object or system, is a concept that has gained popularity throughout various fields of technology (Marr, Bernard 2017). Furthermore, another expectation for the work is that it will be challenging to define general rules for what is sufficient test coverage for a DUT. The role of functional coverage, which is a term related to Coverage Driven Verification (CDV), should be discussed in the context of the verification strategy together with code coverage. Although

the designs that are tested vary in their purpose, it would be beneficial to have metrics for what can be considered a sufficient amount of testing.

### 3 VERIFICATION CONCEPTS OF THIS STUDY

### 3.1 Constrained Random Verification and Coverage Driven Verification

The functional verification methods that are evaluated throughout this thesis are associated with two fundamental verification concepts – Coverage Driven Verification (CDV) and Constrained Random Verification (CRV). These two are linked with each other as they are often applied together. The definitions of these concepts are described in the following paragraphs.

In CDV the quality measure of the test is coverage. The idea of CDV is to create tests that cover as much of the DUT's functionality as possible, which is measured with *code coverage* and *functional coverage*. Code coverage, presented in Chapter 4.3, represents the implicit properties of the DUT, such as the amount of statements in the code that have been exercised throughout the simulation. Functional coverage, however, is explicitly defined by the designer of the test bench. Functional coverage should be based on the requirements of the DUT, and it is therefore unique for each verification environment. Functional coverage for a digital filter could be defined as a set of sine wave frequencies that have to be driven as stimulus to the filter in order to ascertain that the design was adequately tested. A communication protocol implemented in a digital design, however, requires functional coverage that is based on its protocol specifications. The Advanced Extensible Interface, or AXI, for example, has modes for single data word transmission and burst transmission, and therefore requires functional coverage for different transmission sizes (ARM Holdings 2018). Functional coverage will further be described in Chapter 5.3.

What is not defined by the CDV ideology, but what a successful implementation of it requires, is a method of being able to write a large amount of relevant test stimulus. This is where CRV complements CDV. In CRV the stimulus is randomized within limits that are specified by constraints. Throughout this thesis CRV will be used to refer to tests that not only utilize constrained randomization, but also fulfill the CDV principles.

The AXI-protocol implementation mentioned in the previous paragraph required functional coverage for its transmission sizes. In CRV a constraint could be defined as a range that corresponds to the length of data transmissions that are written to the DUT. The constraints are optional and can be specified for each variable in the test bench. In a CRV verification environment stimulus is randomized prior to each transaction, and if the stimulus has constraints, the randomization will conform to these. As randomization automates the stimulus generation, a randomized test bench is also able to drive a greater amount of stimulus than a directed test bench, in which the designer has written the stimulus manually. What a CRV test bench therefore requires is a self-checking mechanism for the response from the DUT. The self-checking component is usually implemented as a comparator that compares the predicted response of the DUT with the actual response received from it. Chapter 3.1.4 describes such implementations in more detail.

### 3.1.1 The Hardwave Verification Language features of SystemVerilog

A language that has become widely popular for verification of digital designs is SystemVerilog, which is based on the Verilog HDL language, but also includes language constructs that are intended for verification. In other words, SystemVerilog is not only a HDL, but also a Hardware Verification Language, or HVL. HVLs include features from high-level programming languages that are useful for the creation of test benches. As test benches do not have to be synthesizable, they do not have to be limited to the syntax of HDLs. HVL features are well suited to the CDV and CRV concepts, as functional coverage, for example, is supported by SystemVerilog through its use of cover-groups, cover points and cross-coverage. Randomization and constraints are also basic features of the SystemVerilog verification language. In SystemVerilog the test bench architectures are often associated with the use of Object-Oriented Programming (OOP). In object-oriented test benches classes correspond to verification components that all have a specified purpose. Furthermore, in these test benches bundles of signals representing interfaces are instantiated and handled as objects. Due to these properties, a test bench structure is achieved that is not only modular, but also reusable for designs with the same interfaces. This reusability has the potential of reducing test bench creation time.

Additionally, as bundles of signals are treated as objects in the test bench, stimulus can easily be written for transactions instead of single signals. This is well suited with the verification concept of Transaction Level Modeling (TLM) that will be described in Chapter 3.1.2. SystemVerilog also includes another beneficial feature for verification, which is unrelated to the features mentioned above: the SystemVerilog Assertions (SVA) subset language.

### 3.1.2 Transaction Level Modeling

TLM, in the context of verification, builds on the idea that stimulus is written to a bundle of signals concurrently, and that the randomization of these signals can be performed as one operation. The purpose of TLM is to create an abstraction layer that is above the signal level of the design. Digital designs that are modular, such as those that are built on IP-cores, often consist of interfaces of coherent signals. In verification of digital designs, identifying these interfaces of the DUT is a prerequisite for building transaction level object-oriented test benches, as transactions in these test benches are instantiated as objects.

Raising the abstraction layer not only makes it easier to simultaneously randomize stimulus, it also saves time during simulation (Bowyer 2006). In CRV test benches certain classes are modeled on the transaction level and are therefore not dependent on the cycle-accurate behavior of the DUT. Consequentially, the procedures of these classes are event-based and do not have to execute unless the specified event is triggered. Additionally, making test bench classes dependent on events rather than cycle-accurate behavior will arguably make the operations of the said classes easier to comprehend. The classes modeled on the transaction level naturally require that there is an underlying set of classes that handle the cycle-accurate behavior of the test bench, but in general, TLM is not intended to verify cycle-accurate behavior of the DUT. Instead, TLM better suits the DUT specifications that are written as higher level requirements, not as cycle-accurate behavior. In other words, the response from the DUT is not assumed to be of importance on every clock cycle of the simulation. Instead, in TLM test benches events

are triggered by specified events of the DUT. The triggered test bench events can be related to self-checking of DUT response or coverage collection.

TLM requires that the self-checking component of the test bench is modeled on a higher abstraction layer than the DUT. The self-checker is therefore programmed with HVL features rather than as HDL code. The DUT functionality determines the level of effort that goes into modeling an equivalent predictor model of the DUT. For example, if the DUT implements an algorithm that was originally modeled and tested in a software language, the software model can be used as a predictor model in the test bench. In such cases the stimulus written to the DUT calls a function that updates the predictor model, which is then compared to the actual response received from the DUT. The predictor model exported from the original software implementation would therefore be reusable for the CRV test bench as it is modeled on the transaction level.

### 3.1.3 The Universal Verification Methodology

UVM is a methodology that implements the concepts presented in the previous subchapters of Chapter 3. The methodology is upheld by Accellera Systems Initiative, a standards organization, and is therefore not tied to a simulator tool distributed by one designated vendor. UVM defines a class-based test bench architecture that is intended to standardize the way that coverage driven constrained random test benches are built. In addition to defining a set of classes for the test bench architecture, UVM also defines a set of phases of testing, such as the build phase, the connect phase, the run phase and the report phase. Out of all UVM phases only the run phase consumes simulation time, and it is therefore the only phase that implements SystemVerilog tasks. The other UVM phases might for example build the test bench prior to the test and gather the coverage report after the test.

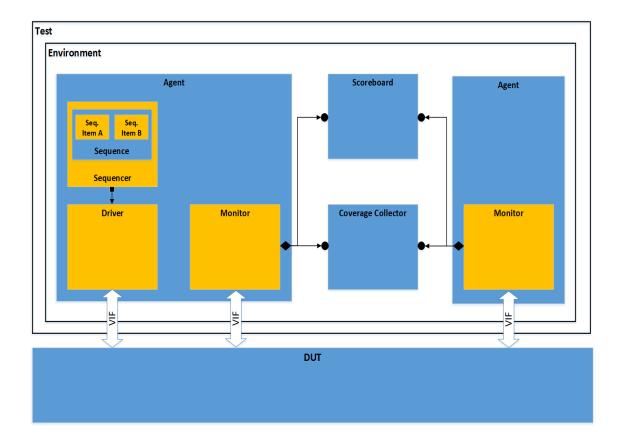

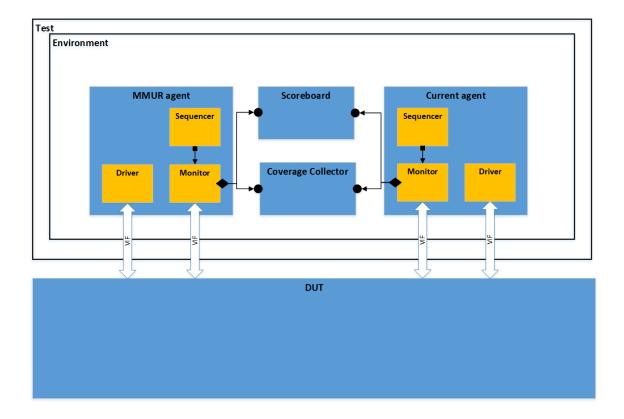

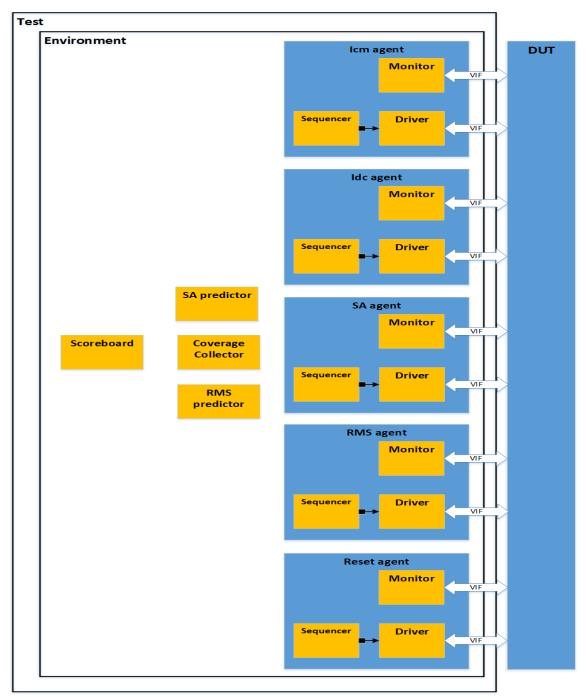

An example of a UVM test bench architecture is depicted in Figure 1. The block diagram contains classes that are generally found in UVM test benches. The exact architecture of a test bench will always depend on the DUT and its interfaces. The following paragraphs will describe the UVM classes in a bottom-up order.

Figure 1. An example of a generic UVM test bench. The test bench resides within the *test* block and it communicates to the DUT via one or several virtual interfaces (VIF), here depicted as bidirectional arrows. The *environment* inside the test contains two *agents*, a *scoreboard* and a *coverage collector*. The leftmost agent contains a *driver*, a *monitor* and a *sequencer*. The sequencer further contains a *sequence* that is built on *sequence items* (Seq. Item A & Seq. Item B). The rightmost agent only contains a monitor and is called a passive agent as it does not drive any data to the DUT. The leftmost agent, by contrast, is an active agent.

The sequence item class is the container for variables that drive and receive DUT signals. Whenever a transaction is created, a new object of the class is instantiated. During the object instantiation the DUT input variables can be randomized. The DUT output variables, on the other hand, do not get randomized as their purpose is to store values that are received from the DUT. The sequence item class does not contain any other functions than its constructor, and it does not implement any tasks during the run phase of a UVM test.

The sequence class is used to model sequences that consist of sequence items. For example, if a communication protocol implements a burst mode for data transmission, the sequence item could represent a data word and the sequence the complete data frame. A UVM sequence is usually parametrized with the type of sequence item it consists of. A sequence can only be built of objects of the parametrized sequence item class and objects of its extended classes. However, it is also possible that a sequence is built on other sequences. Such sequences are called nested sequences.

The sequencer is the container for sequences and sequence items. The sequencer is the class that is called when generation of sequences is desired, and it contains functions for transmitting the sequences towards the DUT. This class usually does not require actions by the designer of the test bench as its functions are provided by the UVM package.

The driver class receives sequences from the sequencer and drives them to the DUT. The driver converts the received sequences, one sequence item at a time, into signal level assignments that are driven to the DUT, after which it gives back control to the sequencer. The driver only drives signals to the DUT and does not monitor received response. An exception to this is handshake communication that requires that a response event from the DUT activates before subsequent signals can be driven to the DUT. Because the driver operates on the signal level it is a part of the UVM test bench environment that is cycle-accurate. The driver therefore contains a task with clock-synchronized logic. The logic of the driver depends on the functionality of the DUT interface that it communicates with.

The monitor class is a component of the UVM test bench that monitors communication to and from the DUT. The monitor also operates on the signal level, however, it usually only triggers on certain events. A triggering event activates assignments that write data to a monitoring stream. The assignments write signal values from the virtual interface to variables of the test bench. In UVM the monitoring stream that is connected to a monitor is known as an *analysis port*. The analysis port is connected to classes in the test bench that handle monitored data. The receiving end of an analysis port is called an

analysis export. A monitor never drives data to the DUT and it can contain multiple analysis ports that are triggered by separate events.

The classes mentioned so far are all contained in an agent class. In UVM the agent is intended to be a reusable verification component and therefore it is recommended that the classes inside it are designed in a generic manner that allows for reuse. The agent is only a container class and its only purpose is to build the components inside it and route analysis ports to its outer boundary. An agent can be either active or passive. An active agent contains a driver and a sequencer while a passive agent does not. The latter can be used for example if an internal signal of the DUT is monitored with a SystemVerilog bind statement and used for coverage collection. Figure 1 contains an active and a passive agent.

The class that encapsulates UVM agents is called the environment. The role of the environment, similarly to the agent, is to build classes inside itself but also to connect analysis ports from outer boundaries of agents to analysis exports of other classes contained within itself. Classes that are not suitable for reuse are generally placed in the environment instead of being placed inside the agents. In the block diagram of Figure 1 two such classes are present in the environment.

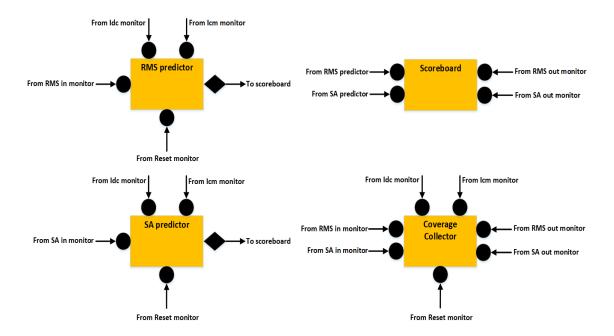

The scoreboard class implements the self-checking of the test. It compares the response of a predictor model with the actual response of the DUT. The predictor model is an equivalent of the DUT that is generally modeled on a higher level of abstraction than the real design. It can be considered as the golden reference for the design that conforms to the design specifications. The predictor model can either be implemented inside the scoreboard or it can be an independent class outside of it. In Figure 1 it is assumed that the predictor model has been implemented internally. The scoreboard can be connected to multiple agents, as can be seen in Figure 1, and it has several methods for handling monitoring events. The functionality of a UVM scoreboard will be described in more detail in Chapter 3.1.4.

In addition to the scoreboard, the environment depicted in Figure 1 also contains a coverage collector. While UVM does not actually define a coverage collector class, it has been named so in Figure 1 for clarity. The UVM cookbook by Mentor Graphics presents two UVM classes that are suitable for coverage collection: the *subscriber* class and the *component* class (Mentor Graphics 2012). The subscriber class extends the component class and offers a simplified method for writing monitored data from one monitor to the coverage collector. The subscriber implements a *write*-function that is automatically called whenever monitored data is received. However, the subscriber is restricted to only one monitoring stream. For coverage collectors that require multiple monitoring streams the UVM cookbook recommends the use of the component class. The coverage collector is the class that contains the SystemVerilog covergroup, coverpoint and cross-coverage statements that gather functional coverage during a test. Whenever a transaction is received from a monitoring stream the functional coverage is updated.

The final class to be presented in this chapter is the test class. The test class is a container for the environment class, which it builds prior to the run phase of a test. Once the simulation proceeds to the run phase, sequencers contained within the agents of the environment are called from the test class. In UVM test completion is controlled with *objections*. Generally, an objection is raised before the sequencers are started in the test class, and dropped once all sequencers have finished their stimulus generation. A dropped objection signals the UVM test bench to proceed from the run phase to its following phases, at which point test reports are gathered and written to files.

### 3.1.4 Self-checking test benches

A successful UVM test requires a self-checking component that automates the task of checking the validity of the DUT response. When building the test bench the self-checking activities of it are arguably the most challenging to design. For the implementation of the predictor model there are not many common guidelines, as the DUT implementations are all unique. What can however be generalized are the methods of how to store the predicted responses, when to trigger a scoreboard comparison and how to do

it. All of these depend on the nature of the transaction stream from the DUT. When designing a self-checking test bench it is important to identify the conditions for when a scoreboard comparison should be made. In this chapter three useful methods for different types of DUTs are presented in Figures 3-5. In the figures the predictor models are not shown and are assumed to be separate from the scoreboards. However, the predictors can also be implemented internally into the scoreboard, in which case the predicted response in the figures would arrive from an internal predictor.

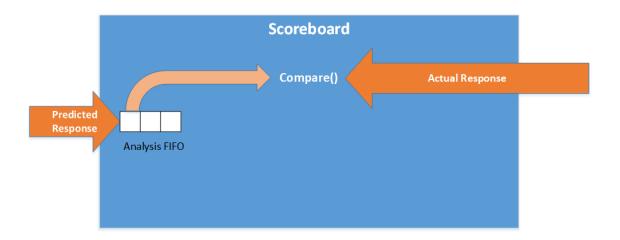

Figure 3. An In Order Scoreboard. A transaction that is written to the DUT results in a predicted response, which is stored in an *Analysis FIFO* in the scoreboard. Once the actual response of the DUT is received, it triggers a comparison with the predicted response. The predicted response is popped from the Analysis FIFO upon being triggered by the actual response.

Figure 3 depicts an In Order Scoreboard for which the order of stimulus and response is known. In its simplest form the scoreboard contains one Analysis FIFO for the predicted response. In this model the Compare-function is called once the response is received from the DUT. If multiple transactions have been stored in the FIFO, the one that was stored first in the buffer is popped. An example use case for the In Order Scoreboard could be an Arithmetic Logic Unit (ALU) that calculates the sum of two numbers.

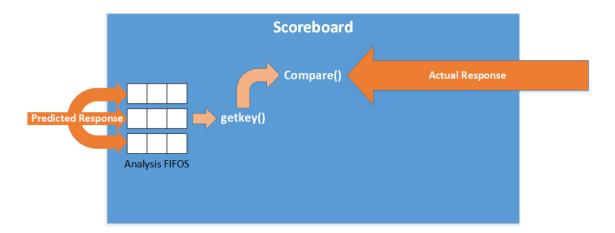

Figure 4. An In Order Array Scoreboard. In this model a transaction that is written to the DUT results in multiple predicted responses, which are all stored in their own Analysis FIFOS. Once an actual response is received from the DUT, a getkey-function is called that determines from which Analysis FIFO a predicted response is retrieved. The predicted response and actual response are then compared.

Figure 4 depicts an In Order Array Scoreboard. This scoreboard type differs from the In Order Scoreboard in that a stimulus results in multiple responses. Using the ALU for the In Order Scoreboard as an example, the In Order Array Scoreboard could be used for a variant of the ALU that calculates the sum, difference and product for two given numbers in parallel. If the ALU only has one output signal for the data, it must contain an additional signal that indicates which operation was performed for its current output. This additional signal would be used in the getkey-function of the scoreboard to determine which Analysis FIFO containing predicted response is popped.

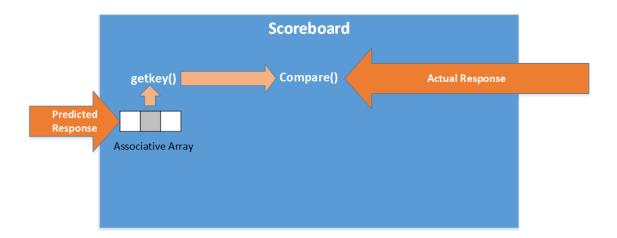

Figure 5. An Out Of Order Scoreboard. In this model the Analysis FIFO of the predicted response has been replaced by an Associative Array. The Associative Array is used as the order of the predicted responses is unknown. Once an actual response is received from the DUT, a getkey–function is called that retrieves a predicted response from the Associative Array. The predicted response and actual response are then compared.

Figure 5 depicts an Out Of Order Scoreboard for which the order of incoming DUT responses cannot be predicted. The Out Of Order Scoreboard utilizes SystemVerilog Associative Arrays instead Analysis FIFOs. Associative Arrays have the benefit of being indexable by types other than integers, and additionally, Associative Arrays do not allocate memory at instantiation – memory is allocated whenever an entry is written to the array. For the Out Of Order Scoreboard the ALU of the previous two paragraphs is no longer a valid example. A design that would require an Out Of Order Scoreboard could be one that contains a buffer for incoming transactions and a state machine that controls the processing of data. If the test bench has no visibility into the design, which is usually the case with UVM test benches, it may not have any knowledge of which of the buffered transactions in the DUT are being handled. Consequently, once a response arrives from the DUT, all of the predicted responses have to be checked for equivalence. In an Associative Array the predicted response could be stored into slots that are indexable by enumerated types. The indices could be for example {valid, buffer\_overflow, protocol\_error, data\_error]. The getkey-function that is called once a DUT response is received would return the type of predicted response that needs to be checked. Each slot in the Associative Array could further contain an array that allows for multiple predicted responses to be active for each enumerated type. If a valid output would be received from the DUT, all predicted responses inside the *valid* slot of the Associative Array would be checked. If no valid entries exist in the Associative Array, an error would be raised.

### 3.2 Temporal Logic verification

In addition to verification on the transaction level, verification can also be performed at a lower level of the design with temporal logic statements. Temporal logic verification is the validation of a design's behavior in terms of time, which in digital designs most often is related to a clock. The following two statements are examples of temporal logic. "I am tired until I rest" and "If I don't eat I will eventually get hungry". The words "until" and "eventually" are modal operators that specify a relation in time between the first part of the statement and the second part of the statement. A digital design can similarly be described by statements that should always, eventually or never hold true. Furthermore, statements can be combined to form layers of temporal logic, for which the validity can be checked with *assertions*. In this thesis verification for temporal logic will not be evaluated, however, as research shows that assertions have become increasingly common in digital design verification, it was decided that an introduction to this topic would be provided. Assertions have been used in conjunction with CRV testing to enhance the quality of testing, and therefore assertions will be discussed in Chapter 8 in the context of potential future research. Two publications are used for reference

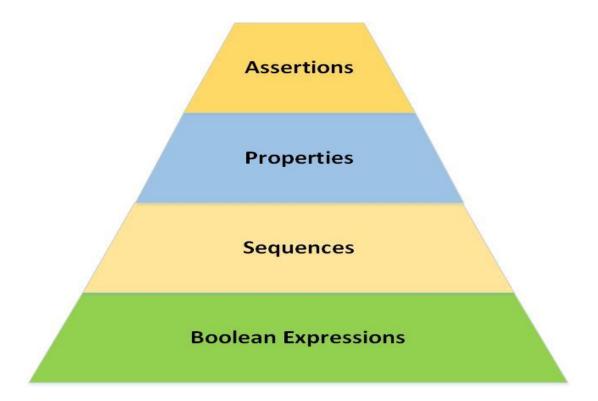

In verification of digital designs or software temporal logic is regarded as a type of formal verification. Common languages used for temporal logic verification of digital design are the Property Specification Language (PSL) and the SystemVerilog subset language SystemVerilog Assertions (SVA). The languages are similar in that they both define a layered structure for modeling a design behavior, often illustrated as a pyramid. An illustration will be given in Figure 6. In both languages the bottommost layer is a Boolean layer that defines statements such as *A and B*. Boolean statement by adding a time relation to it and making an assertion of the resulting temporal statement. In Chap-

ter 3.2.1, an SVA assertion is demonstrated. In this thesis two publications are used as reference on Assertion Based Verification (ABV)(Foster, Krolnik 2008)(Foster, Krolnik, Lacey 2010).

### 3.2.1 SystemVerilog Assertions

SVA is an assertion language that has gained popularity in digital design verification. It separates assertions into two types: *immediate assertions* and *concurrent assertions*. Of these two types the former is a non-temporal assertion while the latter is temporal. Immediate assertions can only be placed within procedural statements, such as always-blocks in SystemVerilog, and they evaluate in zero-time. Concurrent assertions, in contrast, are evaluated over several clock cycles and can be triggered by a certain condition. Out of these two types of assertions, the concurrent assertions are of greater interest for in this study. Assertions, whenever referenced from now on in this study, are therefore assumed to be of the concurrent type.

As described in Chapter 3.2, SVA defines a layered structure for building assertions for temporal statements. The structure is depicted in Figure 6 below.

Figure 6. An illustration of the temporal layers of SystemVerilog concurrent assertions. The bottommost layer defines boolean expressions without time relations. The layer above expands the boolean expressions by creating event sequences of them. The event sequences are specified in terms of clock cycles. Sequences are further used by properties on a layer above. Properties can also be built on properties consisting of sequences. On the topmost layer assertions are made of properties.

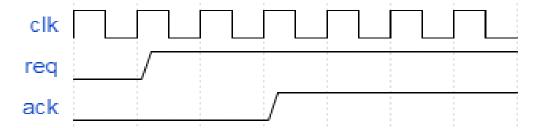

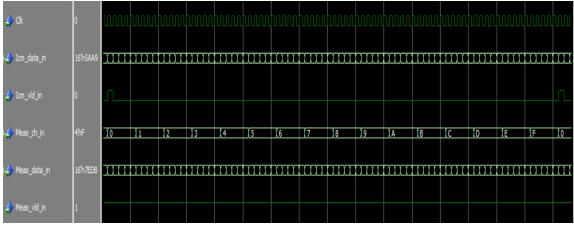

The following paragraphs will give an example of an assertion that is built by the multi-layered approach. The example describes a handshake protocol with a request and acknowledge signal. The concurrent assertion is based on the timing diagram of Figure 7.

Figure 7. A timing diagram of a handshake protocol. When the request signal req rises, the acknowledge signal ack must rise after two clock cycles.

The Boolean expression of this concurrent assertion is not actually necessary, but it will be defined explicitly in this example. The Boolean expression is described by the following line of code.

```

req == 1

```

The Boolean expression can also be simply expressed as req. The following lines of code describe the sequence that is built on top of the Boolean expression. The sequence states that the ack signal must be asserted two clock cycles after req is asserted.

```

sequence req_ack_seq;

req ##2 ack;

endsequence

```

The layer above the sequence layer makes a property of the above sequence. The resulting property is described by the following code segment.

```

property handshake;

@(posedge clk) req_ack_seq;

endproperty

```

The property defined above evaluates the sequence that was modeled on the positive edge of the clock. Below is the code segment that makes an assertion of this property.

```

handshake_assertion: assert property(handshake)

else $error("Handshake error");

```

A concurrent assertion and its underlying temporal statements can either be defined in an interface or a module.

### 3.2.2 Assertions used as protocol checkers

Assertions are valuable in verification whenever design behavior can be described in detail on a cycle-accurate level. The use of assertions therefore requires a knowledge of the design often only possessed by the designer of the DUT. Design documentation of an IP rarely describes the design in detail with timing diagrams that can be used to model assertions. However, interfaces are usually well understood as documents generally contain their timing information. Consequently, assertions can be modeled for these with a relatively small effort and be used as checkers that monitor interaction between the modules of an individual IP-block or the interaction between IP-blocks in a system level design. These checkers increase the visibility into the DUT and may be beneficial for discovering the root cause of a bug. In a test bench without assertions the debugging process arguably requires more effort as the problem cause must first be established before the design can be fixed.

### 3.2.3 Using assertions to complement test benches

Assertions can be used to complement CRV test benches, but if assertions are used in conjunction with a UVM test bench, they must be defined outside of the UVM classes. An assertion IP can be made of a module, or alternatively the assertions can be placed inside a SystemVerilog interface. While the UVM scoreboard checks the response of the DUT on the transaction level, the assertions can check cycle-accurate behavior. The assertions can be of additional value as they can be used to off-load some of the checking that would otherwise have to be implemented in the predictor model. Assertions could also be made during the design phase of the DUT by the designer that has knowledge of the IP.

Assertion IPs can also be used together with test benches created in Verilog or VHDL if a simulator tool is used that supports concurrent assertions. Verilog and VHDL do not have concurrent assertions and are therefore limited to assertions in procedural blocks. Presumably many companies already have an existing system level test bench that is implemented in one of the two aforementioned languages. In such case assertion IPs can be added to the testing without any modifications to the existing test bench. The assertion IPs can be instantiated as additional test bench modules that are simulated in parallel with the top-level module of the system level test bench.

### 4 PRESENT TESTING METHODS OF THE COMPANY

### 4.1 Simulation-based test types in use

At Danfoss Drives the FPGA design team implements three types of simulated tests: the IP-block level test, the system level test and the release test. Out of these three tests only the first two will be covered with case studies in this paper. The release test, which will be excluded from this thesis, is a test that is applied to a system level design before it is handed over to the software team. At present, the purpose of this test is not to extensively test the behavior of the design, but to perform directed tests at features that are known to cause problems in the integration phase of the firmware on the embedded processor and the FPGA. An example of such a feature is the polarity of the *reset*-signal. However, the actual test coverage of the FPGA designs is gathered by the IP-block level test and the system level test. The latter validates the behavior of a system level design that contains multiple IP-blocks. Before an IP-block is tested in the system level test it is assumed that it has already been tested with an IP-block level test bench. The system-level test will also be referred to as the integration test throughout this thesis.

The lowest level of testing is performed at the IP-block level. The IP-block can consist of one or several modules, but it's the smallest unit of reusable logic in an integrated digital design. In the context of testing, the IP-block is easier to test than an integrated system. Apart from containing less logic and having better interface access into the design, the IP-block usually implements a function that is clearly defined. It is also in general easier to gather extensive coverage for an IP-block than during a later phase in the system level test, as the simulation time of an IP is likely to be less than for a larger design. It is customary that the designer of the IP-block, or one of its designers, writes the design specification for the IP-block in question. As the IP-block level test is considered a part of the design process, it is usually implemented by one of the designers responsible for the Register Transfer Level (RTL) logic of the IP.

#### 4.2 Verification methods in use

The tests described in Chapter 4.1 are written in the VHDL language and are mostly performed as test cases with predefined stimulus for which results are validated with VHDL assertions. Procedures and functions are used to generate reusable code for recurring tasks such as generic write and read tasks for certain interfaces. For such interfaces the level of abstraction can be considered to have been raised to the transaction level. Randomization with VHDL has been used for some tests, but in general the current testing methodology can be reviewed as directed testing (Bartley, Galpin & Blackmore 2002). In directed testing the DUT is driven to states with known responses. The behavior for the intended functions of the DUT are known by the designer and should also be documented in the design specification. With directed tests so called corner cases of the design's behavior are generally targeted with dedicated test cases. Corner cases of a design can usually be predicted as they are cases for which bugs are likely to be found. An example of a corner case is the overflow condition for a buffer. As the sequence of events is known in directed testing, and the amount of driven stimulus is generally less than for a random stimulus test bench, debugging also requires less effort than for a randomized test. If extensive coverage of the design is desired, however, the amount of test cases will increase and cause an overhead in the effort required for designing and maintaining the test bench. Directed testing is also potentially hazardous as bugs may remain uncovered for obscure DUT behaviors.

The test benches of the FPGA design team usually consist of a series of test cases that target some functionality of the design. The amount of test cases depends on the complexity of the design. The system level test bench, which has been expanded over time as more features have been designed, currently consists of approximately 30 test cases. For reporting test results, code coverage, which will be described in Chapter 4.3, has been introduced as a metric of testing quality. Code coverage is not intended to indicate whether certain design requirements have been validated through testing or not, it is merely used as an approximation of how much of the RTL code of the design has been covered by the test. The coverage in terms of functionality is currently not reported.

### 4.3 Test reporting with code coverage

The test results are reported for each IP-block as a percentage of achieved code coverage. The code coverage of an IP-block is the combined sum of the coverage gained from the IP-block test and the system level test, which the simulator tool is able to merge. The tool does not raise the total coverage if there are overlaps in covered features, and for example, a statement that is executed in multiple tests is only added once to the total statement coverage. Code coverage is a concept that defines a set of metrics that are measured during a simulation of software, or in this case RTL code. The code coverage that is measured by the FPGA design team at Danfoss Drives is presented in the following paragraphs. As there are variations between the definitions provided by the vendors of the simulator tools, it is worth to notice that the definitions presented here are derived from the Questasim User Manual written by Mentor Graphics (Mentor Graphics 2015: 815-843). The Questasim simulator is the simulator tool that is used during the evaluation of the CRV tests presented this thesis.

Statement coverage counts the execution of statements in the source code. Statement coverage resembles line coverage, with the difference that a line in the source code can consist of several statements. The Mentor Graphics simulators Modelsim and Questasim do not measure line coverage, only statement coverage.

*Branch coverage* counts the execution of branches in if/else and case branch statements. An if-statement with multiple nested else if-statements and an else-statement must have all of its branches executed at least once in order to have been fully covered by branch coverage.

Toggle coverage, in standard mode, regards signals in HDL source code as bit vectors and counts the amount of times each bit has been toggled from 0 to 1 and from 1 to 0. There is also an extended mode of toggle coverage for tri-state signals. These signals have an additional state – the high impedance state Z. The extended mode counts all variations of toggles between 0, 1 and Z. The toggle coverage that is used by default by the FPGA design team at Danfoss Drives is the standard mode.

Finite State Machine coverage counts the amount of times each state and state transition of a Finite State Machine (FSM) has been executed. FSM coverage is useful in RTL design verification as it might reveal logical bugs related to FSMs. Common FSM related bugs include states that are unreachable and state transitions that cannot occur.

Condition coverage counts the execution of each variation of a subexpression in a condition statement, such as an if-statement. For example, the following if-statement written in VHDL contains a subexpression, where signals A and B are one-bit wide signals.

```

if(A and B) then

C <= C+1;

end</pre>

```

The subexpression A and B contains two bits and therefore has four unique input entries. A condition coverage of 100 % would require that all of these have been covered during the simulation. However, an increased amount of input bits leads to an exponential increase in the amount of unique input entries. Standard condition coverage is therefore not an option for subexpressions consisting of bit vectors. As a solution, several vendors offer *Focused Expression Coverage (FEC)* as its default condition coverage. This is also the case with Modelsim and Questasim, the tools used at Danfoss Drives. The following definition of FEC is cited from the Questasim User Manual.

In FEC, an input is considered covered only when other inputs are in a state that allow it to control the output of the expression. Further, the output must be seen in both 0 and 1 states while the target input is controlling it. If these conditions occur, the input is said to be fully covered. The final FEC coverage number is the number of fully covered inputs divided by the total number of inputs (Mentor Graphics 2015).

If a conditional statement contains an expression that consists of several subexpressions, FEC makes a simplification of the full expression before it evaluates each input. For

example, in order to evaluate the FEC condition coverage of input A in the following VHDL if-statement, the expression is first simplified.

The simplified statement of the above if-statement is

The logic expression B and C and D has now been reduced to Expression\_1. In order to fully cover input A, Expression\_1 must be true. When the expression is true, A has exclusive control over the output. Input B is according to the principle of FEC only evaluated when A is true, as the evaluation of the conditional statement moves from left to right. The FEC condition coverage for B is therefore evaluated with the following simplified statement, assuming that A is true.

In the above statement Expression\_2 corresponds to C and D of the original expression.

Expression coverage is the last of the coverage metrics generated by Questasim and Modelsim that is used by the FPGA design team. Expression coverage is similar to condition coverage, except that the statement is a Right Hand Side (RHS) statement of a signal assignment, such as in the following example written in VHDL.

$$A \le B$$

or C and D;

The same problem occurs with expression coverage as with condition coverage. The state space for the input entries can be too vast to cover if the inputs are bit vectors. Expression coverage is therefore by default also gathered as FEC in Modelsim and Questasim.

## 5 VERIFICATION STRATEGY

In this chapter verification strategies for the IP-block test and the integration test will be presented. The presented strategies are intended as guides for creating tests that are based on the functional verification methodologies presented in this thesis. The strategy defines what kind of tests are performed for either the IP-block or the integrated system, what the objective of each test is, how self-checking is implemented and whether randomization and functional coverage is used. Three strategies are introduced in total – two for the IP-block test and one for the integration test. The presented strategies assume a bottom-up order of verification, in which an IP-block is tested before the integration test is performed.

# 5.1 Verification strategies for the IP-block test

The proposed strategies for IP-block testing are based on a black-box approach and are implemented as CRV test benches, UVM being the methodology of choice. In black-box testing it is assumed that the internal functionality of the DUT is non-visible. Therefore, the verification is performed on a higher level of abstraction that only validates the behavior of the DUT through its peripheral signals. White-box verification, on the other hand, assumes that the internal functionality of a design is visible. In white-box verification the behavior of the DUT is validated on a lower level of abstraction within the DUT and on its periphery.

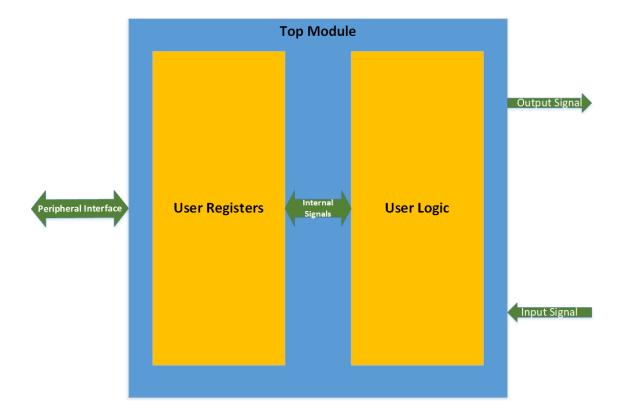

The structure of a generic IP-block is depicted in Figure 9. It will be used as a baseline design for which the verification strategies of the IP-block tests are implemented.

Figure 9. An example of a generic IP-block that contains a submodule for user registers and a submodule for user logic. The peripheral interface, if one exists, usually interacts with the user registers of the IP. The user logic acquires configurations from the user registers through internal signals of the IP. Input and output signals not part of a peripheral interface may also be mapped from the top module directly to the user registers or the user logic.

## 5.1.1 Full IP test bench

In the first proposed strategy the full IP-block will be regarded as the smallest unit that is tested. In designs that interact with software of an embedded processor, IP-blocks can be accessed through a peripheral interface that is usually based on a protocol such as AXI. A commonly used practice is to configure the IP-block from the software with write operations to the user registers of the design. Additionally, if the IP is a co-processing block that is used in conjunction with processes in the software, registers of the IP-block are read by the software, usually by polling the status registers of the IP. The input and output signals of the DUT that are not a part of its peripheral interface are

routed to other IP-blocks in a system-wide design and are therefore not necessarily accessible by the software. The full IP test bench implements a predictor model for the user logic of the IP that also contains a register model for the user registers in the IP.

In Chapter 3.1.4 fundamental self-checking mechanisms of CRV methodologies were introduced. Common for all self-checkers is that there must be a condition that signals the start of an event and another condition to signal a finalized event. The latter will here be referred to as the stop condition. For an IP-block such as the one depicted in Figure 9, the start and stop conditions can be obscure as they are marked by signals that are hidden inside the DUT. A challenge that was encountered at the start of the thesis work was indeed related to these signals. A full IP test bench sends a transaction to a user register that signifies the start of an event. However, the actual start condition can be received by the user logic of the DUT after a delay of a few clock cycles. As the predictor model of the test bench must be synchronized with the DUT in order to be valid, the delay before the event is registered by the predictor model must be equivalent to the delay inside the DUT. This will inevitably mean that the designer of the test bench must have timing specific knowledge of internal logic of the DUT. What can potentially present an even greater challenge for the verification engineer, however, is the stop condition. In designs with a similar design hierarchy as the one depicted in Figure 9, the test bench must poll a status register of the IP that contains a bit that marks a finalized event. Furthermore, if the bit is asserted and the event was finalized, the design might require that one or several user registers containing data are read before the test bench prediction and actual response can be compared. If the test bench stimulates the DUT with a known sequence of transactions, the comparison of the prediction and the response can be triggered from a predetermined read operation that reads the last data item that is required for a comparison. However, if the test bench stimulates the design with a randomized sequence of transactions, the test bench must implement a checking mechanism that assures that a start condition has preceded a stop condition, and that after the stop condition has occured, all registers containing response data must be read before the comparison is performed in the test bench. Consecutively, the complexity of the predictor model in the test bench increases, and with it the time required to design the test bench.

As the write and read operations to the user registers control the behavior of an IP such as the one depicted in Figure 9, limitations can be made for what stimulus would realistically be written to the design. It is therefore proposed that the sequences of the full IP test bench are not fully randomized but split into dedicated test cases. Data can still be randomized as well as the occurrence of certain stimulating events, but the sequencers of the test bench will be more constrained. For example, randomized toggling of the reset signal can be left out of most tests cases. Also, randomized write operations to user registers of the design can be implemented in one dedicated test. Table 1 describes test cases that are generic and that could be implemented instead of one fully randomized test.

Table 1. Examples of generic test cases that can be implemented by the proposed full IP test bench.

| Test type                     | Purpose of the test                                                                                                                                                                                                                 |